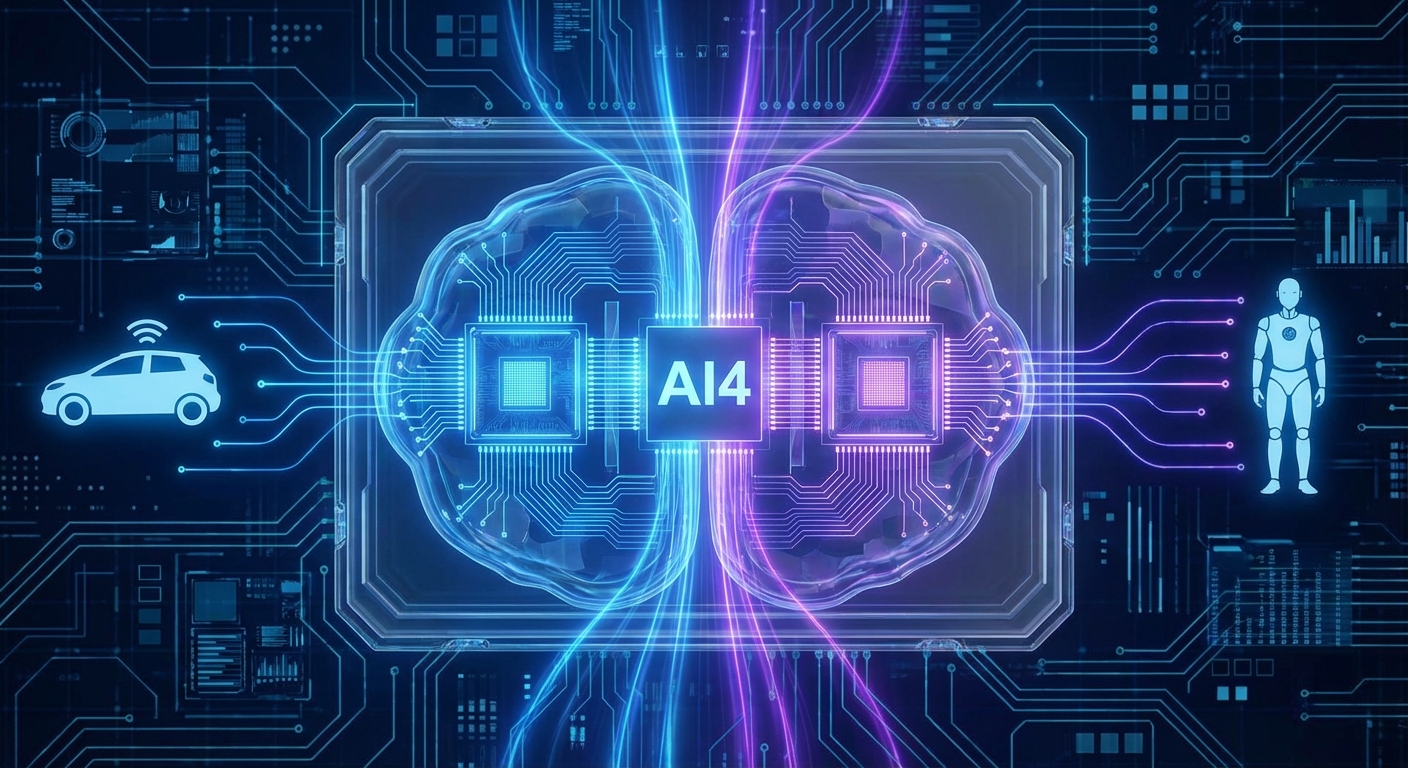

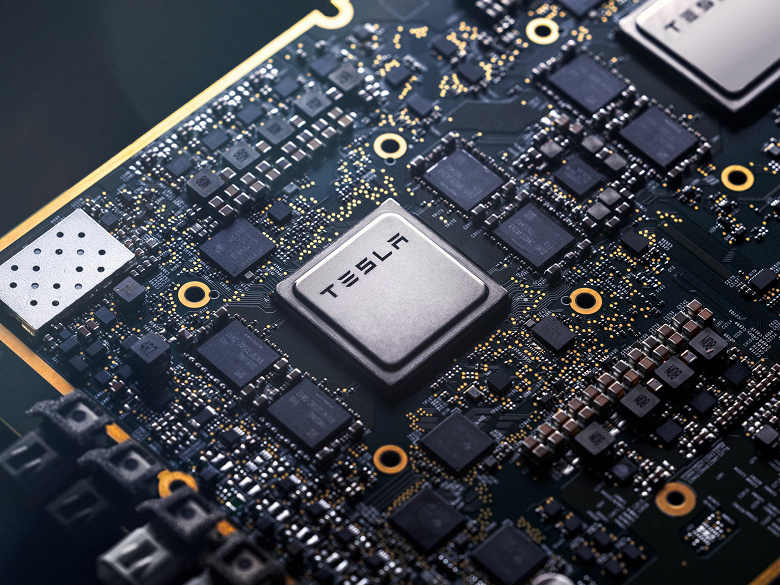

Tesla has detailed its AI4 single-chip system, the core of its Hardware 4.0 (HW4) suite, revealing a foundational focus on fault tolerance through full redundancy. The chip employs a dual-redundancy architecture where two separate computing modules operate in parallel, continuously verifying each other’s calculations. In the event one module encounters an error, the second is designed to take over control instantaneously. This approach is critical for the safety and reliability of Tesla’s Full Self-Driving (FSD) system, where computational failures are unacceptable. This built-in redundancy ensures operational continuity, significantly enhancing safety by minimizing the risk of critical function failure while the vehicle is in motion.

The Architecture of Reliability

The AI4 system represents a strategic evolution of Tesla’s in-house silicon efforts. Manufactured on Samsung’s mature 7nm process, it prioritizes reliability and cost-effectiveness over chasing peak theoretical performance. The computer features 20 ARM Cortex-A72 CPU cores, an increase from the 12 in the previous generation, with a maximum frequency of 2.35 GHz. While its raw performance is estimated at around 100-150 TOPS (Trillion Operations Per Second), its key design choice lies in memory bandwidth. By using GDDR6 memory, AI4 achieves a bandwidth of approximately 384 GB/s, a necessary trade-off to process the massive streams of high-resolution video from the vehicle’s cameras, which is central to Tesla’s vision-only autonomy strategy.

Powering FSD and Optimus

The AI4’s applications extend beyond Tesla’s vehicle lineup, forming a unified hardware foundation for the company’s broader AI ambitions. For FSD, the dual-SoC design is intended to eliminate single points of failure, a fundamental requirement for advancing toward higher levels of driving automation. Beyond the car, the same hardware powers the Tesla Optimus humanoid robot. This shared platform allows for streamlined development, as advancements in AI processing and neural network efficiency can be deployed across both automotive and robotic applications.

The Competitive Landscape

Tesla’s vertically integrated approach with AI4 contrasts sharply with the strategies of its main competitors, who are positioning themselves as platform providers for the wider automotive industry.

NVIDIA’s Drive Thor

NVIDIA’s Drive Thor platform is AI4’s most formidable rival. Built on TSMC’s advanced 4N process, Thor boasts a staggering theoretical performance of up to 2,000 TFLOPS and utilizes modern, server-grade ARM Neoverse CPUs. It is designed as a comprehensive, whole-car computer capable of managing both autonomous driving and in-cabin infotainment, attracting a wide range of automakers like BYD, Lucid, and Zeekr.

Mobileye and Qualcomm

Other key players are pursuing different paths. Mobileye, a former Tesla partner, emphasizes what it calls “True Redundancy” by fusing data from cameras with radar and LiDAR, a different approach to safety than Tesla’s vision-only system. Meanwhile, Qualcomm’s Snapdragon Ride platform is being adopted by automakers like BMW, positioning Qualcomm as an “arms dealer” of autonomous technology that enables legacy manufacturers to compete with Tesla’s capabilities.

A Look to the Future: Beyond AI4

The AI4 chip is a crucial component of Tesla’s current ecosystem, but it is also a stepping stone. The company has already begun quietly rolling out an incremental update known as AI4.5 in some new vehicles, likely as a bridge to its next major hardware generation. The true successor, the AI5 chip, is expected to enter production in late 2026 or early 2027. Elon Musk has suggested that AI5 will offer a performance leap of 3 to 5 times over AI4, and it is slated to be the brain behind the upcoming Tesla Cybercab and more advanced versions of the Optimus robot. Looking further, Musk has outlined an aggressive roadmap for future chips like AI6 and beyond, aiming for a rapid 9-month design cycle to accelerate AI development across all of Tesla’s products.