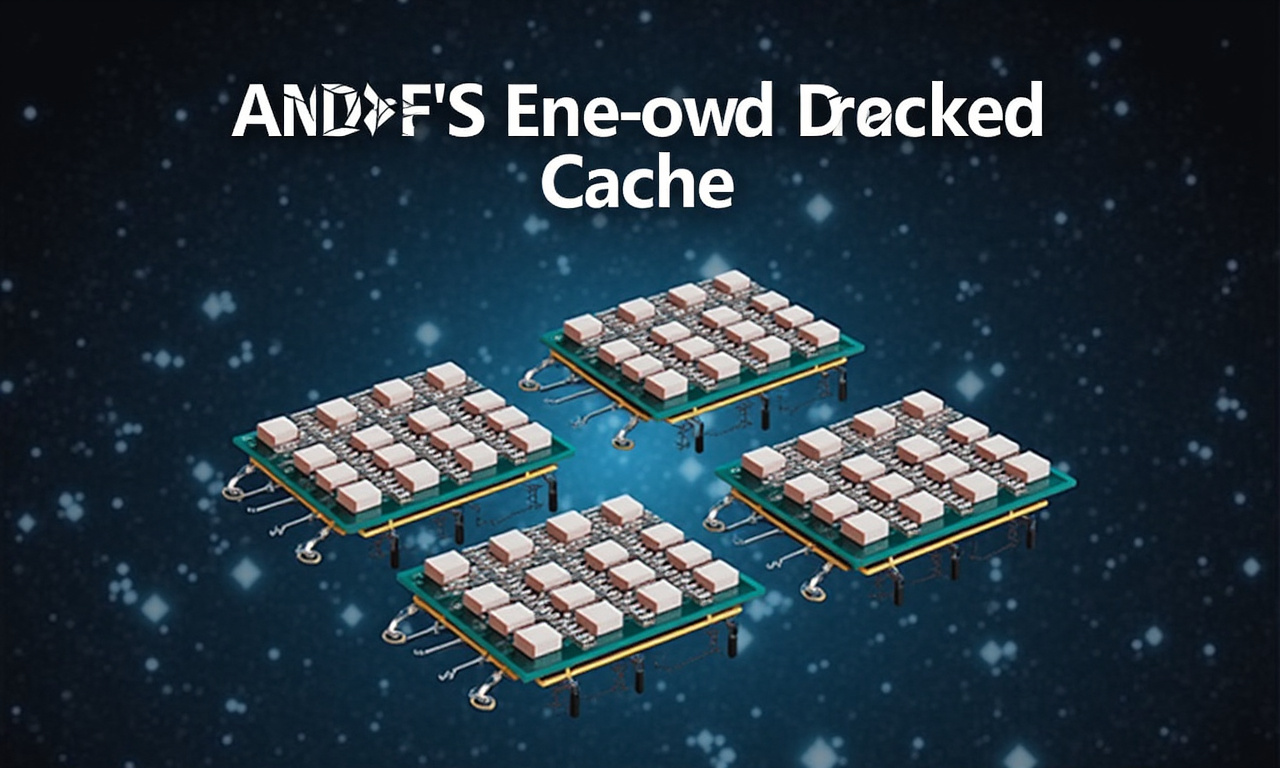

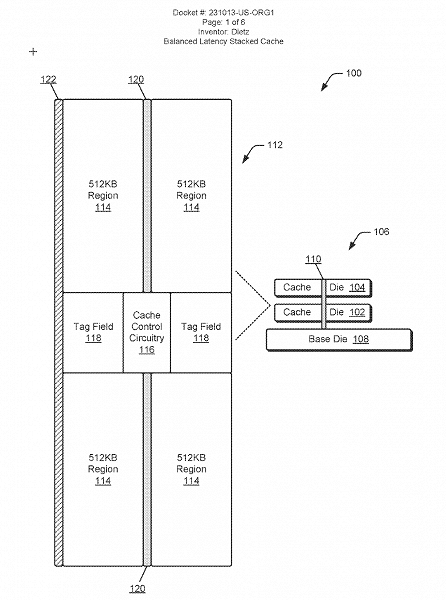

AMD has been releasing Ryzen X3D processors with additional third-level cache for three generations now. Recent patents reveal that AMD is working on similar technology for L2 cache. A patent titled Balanced Latency Stacked Cache describes methods for implementing cache memory with balanced latency and stacking, where the stacking system includes a first cache die and at least a second cache die stacked with the first one.

As with L3, this solution will allow the L2 cache volume to be increased by means of chips placed above or below the main die. It is worth remembering that the volume of second-level cache is much smaller, so the chip is likely to be very small. For example, the flagship Ryzen 9 9950X has 64 MB of L3 cache and only 16 MB of L2 cache. Nevertheless, the patent makes it clear that AMD is considering options for placing multiple memory chips to increase L2 cache. Industry experts speculate that the successful implementation of such a technology could give AMD a competitive edge, especially in performance-demanding applications.

In particular, one example uses a cache module with four areas of 512 KB, totaling 2 MB of L2. This complex can be expanded as necessary, with block diagrams showing examples with volumes of up to 4 MB. However, it’s still a patent at this stage, so it’s unclear if AMD will ever implement such a solution.